# Tribhuvan University

# Institute of Science and Technology Bachelor of Science in Computer Science and Information Technology

Course Title: Digital LogicFull Marks: 60 + 20 + 20Course No.: CSC111Pass Marks: 24 + 8 + 8

Nature of the Course: Theory + Lab Credit Hrs: 3

**Semester:** I

**Course Description:** This course covers the concepts of digital logic and switching networks. The course includes the fundamental concepts of boolean algebra and its application for circuit analysis, multilevel gates networks, flip-lops, counters logic devices and synchronous and asynchronous sequential logic and digital integrated circuits.

Course Objectives: The main objective of this course is to introduce the basic tools for the design of digital circuits and introducing methods and procedures suitable for a variety of digital design applications.

#### **Course Contents:**

| Units                                       | Topics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Hours     | Remarks         |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|

| 1. Binary systems                           | <ol> <li>Digital systems         <ul> <li>Digital and analog system</li> <li>Block diagram of digital computer advantage/disadvantages of digital system</li> </ul> </li> <li>Binary Numbers         <ul> <li>Number system (binary, decimal, octal, hexadecimal), importance of number system</li> <li>Number base conversion (binary to decimal, octal &amp; hexadecimal and viceversa etc.)</li> <li>Complements- r's, (r-1)'s</li> <li>Complement methods of addition/subtraction (r's &amp; (r-1)'s)</li> </ul> </li> <li>Binary Systems</li> </ol> | Hours 1 4 | Remarks 6 hours |

| 2.<br>Boolean<br>algebra and<br>Logic Gates | <ul> <li>BCD codes, error-detection codes, reflected code, alphanumeric codes (ASCII, EBCDIC)</li> <li>Basic definition of Boolean Algebra</li> <li>Introduction</li> <li>Common postulates</li> <li>Basic Theory of Boolean Algebra</li> </ul>                                                                                                                                                                                                                                                                                                          | 1         | 5 hours         |

|                                             | <ul><li>Duality theorem</li><li>Basic theorems</li><li>De-Morgans theorem</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                 |

|                | 3. Boolean Function                                                        | 1 |         |

|----------------|----------------------------------------------------------------------------|---|---------|

|                | <ul> <li>Boolean function and truth table</li> </ul>                       |   |         |

|                | <ul> <li>Algebraic manipulation and simplification</li> </ul>              |   |         |

|                | of Boolean function                                                        |   |         |

|                | <ul> <li>Complement of a function</li> </ul>                               |   |         |

|                | <ul> <li>Logic operations and Logic gates</li> </ul>                       |   |         |

|                | <ul> <li>Logic circuit, AND, OR, NOT operation</li> </ul>                  |   |         |

|                | <ul> <li>Logic Gates: Basic gates, universal gates,</li> </ul>             |   |         |

|                | Ex-OR, Ex-NOR Buffer                                                       |   |         |

|                | <ul> <li>Implementation of Boolean function using</li> </ul>               |   |         |

|                | gates                                                                      |   |         |

|                | 4. Logic operations and Logic gates                                        | 2 | •       |

|                | <ul> <li>Logic circuit, AND, OR, NOT operation</li> </ul>                  |   |         |

|                | <ul> <li>Logic gates: Basic gates, Universal gates,</li> </ul>             |   |         |

|                | Ex-OR, Ex-NOR, Buffer                                                      |   |         |

|                | <ul> <li>Implementation of Boolean function using</li> </ul>               |   |         |

|                | gates                                                                      |   |         |

|                | <i>6</i>                                                                   | 2 | -       |

|                | 5. Integrated Circuits                                                     |   |         |

|                | <ul> <li>Concept of DIP, SIMM, linear and digital</li> </ul>               |   |         |

|                | ICs                                                                        |   |         |

|                | • RTL, TTL, MOS, CMOS, I <sup>2</sup> L                                    |   |         |

|                | <ul> <li>Positive and Negative Logic</li> </ul>                            |   |         |

|                | <ul><li>Special Characteristics</li></ul>                                  |   |         |

|                | <ul> <li>Characteristics of IC logic Families</li> </ul>                   |   |         |

| 3.             | 1. SOP and POS                                                             | 2 | 5 hours |

| Simplification | • SOP, POS, min-term, max-term, standard                                   | 2 | 3 nours |

| of Boolean     | and canonical form                                                         |   |         |

| Functions      | <ul> <li>Simplification of SOP and POS function</li> </ul>                 |   |         |

|                | using Boolean algebra                                                      |   |         |

|                | 2. K-map                                                                   | 2 | -       |

|                | Importance of k-map                                                        | _ |         |

|                | <ul> <li>Simplification of SOP and POS form</li> </ul>                     |   |         |

|                | <ul> <li>2 and 3 variable k-map</li> </ul>                                 |   |         |

|                | <ul><li>4 variable k-map</li></ul>                                         |   |         |

|                | <ul><li>Don't care combination</li></ul>                                   |   |         |

|                | 3. NAND and NOR implementation                                             | 1 | -       |

|                | NAND and NOR conversion                                                    | 1 |         |

|                | <ul> <li>Rules for NAND and NOR implementation</li> </ul>                  |   |         |

|                | <ul> <li>Implementation of SOP and POS logic</li> </ul>                    |   |         |

|                | expressions using NAND, NOR and basic                                      |   |         |

|                | gates                                                                      |   |         |

| 4.             | 1. Design Procedure                                                        | 1 | 5 hours |

| Combinational  | Design Flocedure     Definition of combinational logic circuit             | 1 | 3 Hours |

| Logic          | <ul> <li>Design procedure</li> </ul>                                       |   |         |

| Logic          | <ul> <li>Besign procedure</li> <li>Realization / Implementation</li> </ul> |   |         |

|                |                                                                            | 1 | -       |

|                | 2. Adders/Sub-tractors                                                     | 1 |         |

|                | Half Adder - definition, truth table, logic  diagram implementation        |   |         |

|                | diagram, implementation                                                    |   |         |

|                | • Full Adder - definition, truth table, logic                                |     |         |

|----------------|------------------------------------------------------------------------------|-----|---------|

|                | diagram, implementation                                                      |     |         |

|                | Half sub-tractor                                                             |     |         |

|                | • Full sub-tractor                                                           | 1   | -       |

|                | 3. Code Conversion                                                           | 1   |         |

|                | • General Concept                                                            |     |         |

|                | Code conversion – BCD to Excess-3  A polygic Proceedure                      | 1   | -       |

|                | 4. Analysis Procedure                                                        | 1   |         |

|                | • General concept                                                            |     |         |

|                | Steps in analysis     Obtaining Realess functions from logic                 |     |         |

|                | <ul> <li>Obtaining Boolean functions from logic diagram</li> </ul>           |     |         |

|                | Obtaining truth table from logic diagram                                     |     | _       |

|                | 5. NAND, NOR, Ex-OR circuits                                                 | 1   |         |

|                | <ul> <li>Concept of multi-level NAND and NOR circuits</li> </ul>             |     |         |

|                | <ul> <li>Implementation of basic operations using universal gates</li> </ul> |     |         |

|                | Block diagram method of Boolean function                                     |     |         |

|                | implementation                                                               |     |         |

|                | • Realization of Ex-OR using basic gates and                                 |     |         |

|                | universal gates                                                              |     |         |

|                | <ul> <li>Parity generator, Parity checker</li> </ul>                         |     |         |

| 5.             | 1. Adders                                                                    | 1   | 8 hours |

| Combinational  | <ul> <li>4-bit parallel binary adder</li> </ul>                              |     |         |

| Logic with MSI | <ul> <li>Decimal Adder – BCD Adder</li> </ul>                                |     | _       |

| and LSI        | 2. Magnitude Comparator                                                      | 2   |         |

|                | <ul> <li>Definition</li> </ul>                                               |     |         |

|                | 4-bit Magnitude Comparator                                                   |     |         |

|                | 3. Decoder                                                                   |     |         |

|                | Definition of Encoder and Decoder                                            |     |         |

|                | • 3-to-8 line decoder                                                        | 1   | _       |

|                | 4. Multiplexers                                                              | 1   |         |

|                | <ul> <li>Meaning of multiplexing and demultiplexing</li> </ul>               |     |         |

|                | <ul><li>4-to-1 line multiplexer</li></ul>                                    |     |         |

|                | 5. Read-Only-Memory (ROM)                                                    | 1   |         |

|                | Types of ROM                                                                 | 1   |         |

|                | <ul> <li>Combinational logic implementation of</li> </ul>                    |     |         |

|                | ROM                                                                          |     |         |

|                | 6. Programmable Logic Array (PLA)                                            | 1.5 | 1       |

|                | Difference between ROM and PLA                                               | 1.0 |         |

|                | Block diagram of PLA                                                         |     |         |

|                | <ul> <li>PLA Program Table</li> </ul>                                        |     |         |

|                | <ul> <li>Implementation of PLA</li> </ul>                                    |     |         |

|                | 7. Programmable Array Logic (PAL)                                            | 1.5 | 1       |

|                | PAL programming table                                                        |     |         |

|                | • Circuit design                                                             |     |         |

|                |                                                                              |     |         |

| i              |                                                                              | 1   |         |

|               | 1 Elia Elia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2 | 101      |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|

| 6.            | 1. Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3 | 10 hours |

| Synchronous   | <ul> <li>Definition of sequential circuit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |          |

| and           | <ul> <li>RS flip-flop, clocked RS FF</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |          |

| Asynchronous  | <ul> <li>D flip-flop, J-K flip-flop, T flip-flop, J-K</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |          |

| Sequential    | Master Slave flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |          |

| Logic         | 2. Triggering of flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2 |          |

|               | • Clock pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |          |

|               | <ul> <li>Positive and negative edge triggering</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |          |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |          |

|               | <ul> <li>Clocked J-K FF, edge triggered D FF</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |          |

|               | Direct inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |          |

|               | 3. Design with state equations and state reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3 |          |

|               | table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |          |

|               | <ul> <li>State table</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |          |

|               | <ul> <li>State diagram</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |          |

|               | <ul> <li>State equation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |          |

|               | <ul> <li>State reduction and assignment</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |          |

|               | 4. Design procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |          |

|               | Design procedure of sequential circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |          |

|               | 5. Introduction to Asynchronous circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2 |          |

|               | Basic definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |          |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |          |

|               | • Difference between Synchronous and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |          |

|               | Asynchronous circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |          |

|               | <ul><li>State table</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |          |

|               | <ul> <li>State diagram</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |          |

|               | <ul> <li>State equation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |          |

|               | <ul> <li>Circuits with latches.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |          |

| İ             | CIT OF THE TANGETON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |          |

|               | CITCHIO HIM IMPIRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |          |

| 7.            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 | 6 hours  |

|               | 1. Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 | 6 hours  |

| Registers and | Registers     Introduction to register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 | 6 hours  |

|               | <ul> <li>1. Registers</li> <li>• Introduction to register</li> <li>• Shift registers – serial-in serial-out,</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 | 6 hours  |

| Registers and | <ul> <li>1. Registers</li> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 | 6 hours  |

| Registers and | <ul> <li>1. Registers</li> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3 | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                   |   | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                    |   | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                   |   | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                    |   | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> <li>Synchronous Counters</li> </ol>                                                                                                                                                                                                                                                                                                                                      |   | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> <li>Synchronous Counters         <ul> <li>Binary counter</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                          |   | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> <li>Synchronous Counters         <ul> <li>Binary counter</li> <li>Binary up/down counter</li> <li>BCD counter</li> </ul> </li> </ol>                                                                                                                                                                                                                                     |   | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> <li>Synchronous Counters         <ul> <li>Binary counter</li> <li>Binary up/down counter</li> <li>BCD counter</li> </ul> </li> <li>Timing sequences</li> </ol>                                                                                                                                                                                                           | 3 | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> <li>Synchronous Counters         <ul> <li>Binary counter</li> <li>Binary up/down counter</li> </ul> </li> <li>Timing sequences         <ul> <li>Word time generation</li> </ul> </li> </ol>                                                                                                                                                                              | 3 | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> <li>Synchronous Counters         <ul> <li>Binary counter</li> <li>Binary up/down counter</li> </ul> </li> <li>Timing sequences         <ul> <li>Word time generation</li> <li>Timing signals</li> </ul> </li> </ol>                                                                                                                                                      | 3 | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> <li>Synchronous Counters         <ul> <li>Binary counter</li> <li>Binary up/down counter</li> </ul> </li> <li>Timing sequences         <ul> <li>Word time generation</li> <li>Timing signals</li> <li>Johnson's counter</li> </ul> </li> </ol>                                                                                                                           | 3 | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> <li>Synchronous Counters         <ul> <li>Binary counter</li> <li>Binary up/down counter</li> <li>BCD counter</li> </ul> </li> <li>Timing sequences         <ul> <li>Word time generation</li> <li>Timing signals</li> <li>Johnson's counter</li> </ul> </li> <li>Memory Unit</li> </ol>                                                                                 | 3 | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> <li>Synchronous Counters         <ul> <li>Binary counter</li> <li>Binary up/down counter</li> <li>BCD counter</li> </ul> </li> <li>Timing sequences         <ul> <li>Word time generation</li> <li>Timing signals</li> <li>Johnson's counter</li> </ul> </li> <li>Memory Unit         <ul> <li>Introduction to memory unit</li> </ul> </li> </ol>                        | 3 | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> <li>Synchronous Counters         <ul> <li>Binary counter</li> <li>Binary up/down counter</li> <li>BCD counter</li> </ul> </li> <li>Timing sequences         <ul> <li>Word time generation</li> <li>Timing signals</li> <li>Johnson's counter</li> </ul> </li> <li>Memory Unit         <ul> <li>Introduction to memory unit</li> <li>Block diagram</li> </ul> </li> </ol> | 3 | 6 hours  |

| Registers and | <ol> <li>Registers         <ul> <li>Introduction to register</li> <li>Shift registers – serial-in serial-out, parallel-in parallel-out, serial-in parallel-out, parallel-in serial-out</li> </ul> </li> <li>Ripple Counters         <ul> <li>Definition of counter, ripple and synchronous counter</li> <li>Asynchronous counter – BCD ripple counter, Binary ripple counter</li> </ul> </li> <li>Synchronous Counters         <ul> <li>Binary counter</li> <li>Binary up/down counter</li> <li>BCD counter</li> </ul> </li> <li>Timing sequences         <ul> <li>Word time generation</li> <li>Timing signals</li> <li>Johnson's counter</li> </ul> </li> <li>Memory Unit         <ul> <li>Introduction to memory unit</li> </ul> </li> </ol>                        | 3 | 6 hours  |

| Integrated circuit memory |  |  |

|---------------------------|--|--|

|                           |  |  |

|                           |  |  |

|                           |  |  |

#### **Text Books:**

1. M. Morris Mano, "Digital Logic & Computer Design"

#### **Reference Books:**

- 1. Brain Holdsworth, "Digital Logic Design", Elsevier Science.

- 2. John Patrick Hayes, "Introduction to Digital Logic Design", Addison-Wesley.

- 3. M. Morris Mano and Charles Kime, "Logic and Computer Design Fundamentals", Pearson New International.

# **Laboratory works:**

Introduction to logic gates with IC pin details and verify the truth table using bread board.

- 1. Use any one simulator to simulate the basic logic circuits functions.

- 2. Design of half adder, full adder, subtractor using basic logic gates.

- 3. Study and verification of 3-8 decoder using IC.

- 4. Study and verification of 8-3 encoder using IC

- 5. Implementation of 4-1 Mux using IC

- 6. Implementation of 1-4 DeMux using IC

- 7. Implementation of 7 Segment Display

- 8. Verification of Flip flop

- 9. Design and verification of Up counter/Down counter

- 10. Design and verification of Shift Register

## **Required devices:**

- 1. Bread board

- 2. Multimeters

- 3. IC's/Logic Gates

#### **Model Question:**

#### **Group A (Long Answer Question Section)**

#### Attempt any TWO questions.

(2x10=20)

- 1. Implement the following function  $F=\Sigma(0,1,3,4,7)$  using

- a) Decoder

- b) Multiplexer

- c) PLA

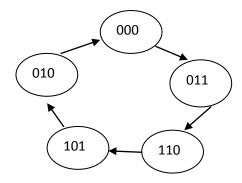

- 2. Differentiate between synchronous and asynchronous sequential circuit. Design a counter as shown in the state diagram below

3. Explain different types of shift registers with necessary diagrams.

#### **Group B (Short Answer Question Section)**

## Attempt any EIGHT questions.

(8x5=40)

- 4. Convert (2AC5)16 to decimal, octal and binary.

- 5. What do you mean by encoder? Design 3 to 8 line encoder.

- 6. Design a combinational circuit that multiplies 2-bit numbers, a1a0 and b1b0 to produce a 4-bit product, c3c2c1c0. Use AND gates and half-adders.

- 7. Design a circuit which produces 2's complement of the given four bit binary digit.

- 8. Implement full adder using decoder with truth table and logic diagram.

- 9. Design a circuit that produces the square of three bit number using ROM?

- 10. Use K-map to simplify the given function in POS. Implement the simplified function using 2-input NOR-NOR gate only.

$$F = \prod M (0,1,2,9,10,11,14)$$

And with don't care conditions

$$D = \prod M (7,8,12)$$

- 11. Discuss race condition in J-K Flip flop and methods to overcome it.

- 12. Write Short notes on (Any two)

- a) Coding system in logic design

- b) Error-detection code

- c) Universal Gates